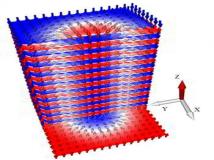

基于FPGA的分布式共享内存架构支持CXL 2.0+规范论文提出了支持CXL 2.0+规范的基于FPGA的分布式共享内存架构。

研发:向基于CXL的计算内存卸载

本工作首先探讨了这些权衡,并展示了它们对具有多样化数据和处理需求工作负载的端到端性能和系统效率的影响。

ArXiv发表了一篇由美国佐治亚理工学院计算机科学学院的Suyeon Lee、韩国城南SK海力士记忆系统研究的朴康奎、韩国韩国SK海力士的申光植,以及美国佐治亚理工学院亚特兰大计算机科学学院的Ada Gavrilovska撰写的文章。

摘要:“基于CXL的计算存储器(CCM)实现了扩展远程内存中的近内存处理,为解决与拆分内存系统相关的数据移动成本和加速整体性能提供了机会。然而,现有的作卸载机制无法利用基于不同CXL协议的不同模型之间的权衡。本研究首先考察了这些权衡,并展示了它们对端到端性能和系统效率的影响,适用于数据和处理需求多样的工作负载。我们提出了一种新颖的“异步回流”协议,通过在底层CXL协议之上精心叠加数据和控制传输作。我们设计了KAI,一个实现异步反向流模型的系统,支持异步数据流动和主机-CCM交互中的轻量流水线。总体来看,KAI将端到端运行时间缩短了最多50.4%,CCM和主机空闲时间平均减少了22.11倍和3.85倍。”

研发:基于CXL支持的GPU-NDP系统中的上下文感知专家混合推断

作者开发了一套上下文感知的MoE系统,利用预填充阶段激活统计指导解码阶段专家的配置,动态将热专家钉在GPU侧HBM,并将其余部分映射到CXL-NDP。

ArXiv发表了一篇文章,作者包括范泽豪、刘振宇,美国纽约州特洛伊伦斯勒理工学院、刘云珍,美国马萨诸塞大学阿默斯特分校,美国纽约州特洛伊,伦斯勒理工学院侯雅月,瑞士IBM欧洲研究院Hadjer Benmeziane,美国纽约州约克镇高地,以及 刘刘,伦斯勒理工学院,纽约州特洛伊,美国。

摘要:“专家混合(MoE)模型通过条件计算扩展大型语言模型,但一旦专家权重超过GPU内存容量,推断就会受内存限制。在这种情况下,权重必须卸载到外部存储器,取权重会产生昂贵且反复的传输。我们通过采用CXL附加近数据处理(CXL-NDP)作为卸载层,现场执行冷专家,将昂贵的参数移动转化为更便宜的激活移动。与以往GPU-NDP系统大多依赖上下文无关且被动不同,我们开发了一个上下文感知的MoE系统,利用预填充阶段激活统计指导解码阶段专家的配置,动态将热专家钉在GPU侧的HBM,其余的映射到CXL-NDP。为了满足NDP有限的计算吞吐量,我们引入了上下文感知混合精度量化,根据预填充阶段分配每位专家的位宽(1-4位)。由此产生的 MoE 推理系统在最小化跨设备移动的同时,重叠 GPU 和 NDP 执行。对GPU-NDP系统的评估显示,我们的方法比最先进方法实现了多达8.7倍的解码吞吐量提升,同时平均准确率仅下降0.13%。

《R&D:部分缓存相干CXL共享内存索引构建指南》

论文重点在PCC平台上构建一致且高效的索引。

ArXiv发表了一篇由吴芳诺、董明凯、蔡文俊、颜景生和陈海博撰写的文章,作者是中国上海交通大学并行与分布式系统研究所(IPADS)。

摘要:“emph{部分缓存-一致性(PCC)}模型仅在核心子集内维持硬件缓存一致性,使得与新兴的内存互联技术如Compute Express Link(CXL)实现大规模内存共享成为可能。然而,PCC对全局缓存一致性的放松会损害现有单机软件的正确性。”

“本文重点是构建PCC平台上一致且高效的指数。我们提出,现有为缓存一致性平台设计的索引可以在 PCC 平台上按照 SP 指南保持一致,即根据索引的并发控制机制识别 emph{sync-data} 和 emph{protected-data},并相应同步。然而,按照SP指南进行转换会带来性能开销。为减轻开销,我们识别了PCC平台上若干独特性能瓶颈,并提出了P^3指南(即使用Out-of-underline{P}lace更新、Reunderline{P}licated共享变量、Sunderline{P}分隔式读取)以提高PCC平台上转换索引的效率。

“根据SP和P^3的指导原则,我们为PCC平台转换和优化了两个索引(CLevelHash和BwTree)。评估显示,按照P^3指南,转换后的索引吞吐量提升可达16倍,且优化后的索引比基于消息传递和基于拆分内存的索引高出多达16倍和19倍。“

研发:Beluga,基于CXL的内存架构,实现可扩展且高效的LLM KVCache管理

作者提出了Beluga,一种新颖的内存架构,使GPU和CPU能够通过CXL交换机访问共享的大规模内存池。

ArXiv发表了一篇文章,作者为杨欣俊,阿里巴巴云计算,美国加州阳光谷,青大胡,阿里巴巴云计算,中国杭州,阿里巴巴云计算,李俊如,阿里云计算,北京,中国,李菲菲,朱一聪,阿里巴巴云计算,杭州,中国,宇奇周,阿里巴巴云计算,中国北京,千鲁林,建岱,阿里巴巴云计算,中国杭州,杨孔, 张嘉宇,阿里云计算,上海,徐国强,阿里云计算, 杭州,以及刘强,阿里云计算,中国深圳。

摘要:“LLM模型规模的快速增长以及对长上下文推理需求的增长,使内存成为GPU加速服务系统中的关键瓶颈。虽然GPU上的高带宽内存(HBM)提供快速访问,但其有限的容量需要依赖主机内存(CPU DRAM)来支持更大的工作集,如KVCache。然而,最大DRAM容量受限于每个CPU插槽内存通道数量有限。为克服这一限制,现有系统通常采用基于RDMA的拆分内存池,这带来了高访问延迟、复杂的通信协议和同步开销等重大挑战。幸运的是,新兴的CXL技术为KVCache设计带来了新机遇。本文提出了Beluga,一种新型内存架构,使GPU和CPU能够通过CXL交换机访问共享的大规模内存池。通过支持CXL结构上的原生加载/存储访问语义,我们的设计实现了近本地内存延迟,同时降低编程复杂度并最小化同步开销。我们对基于商用CXL交换机的内存池进行了系统性表征,并提出了一套设计指南。基于Beluga,我们设计并实现了Beluga-KVCache,这是一个专门用于管理大型语言模型推理中大规模KVCache的系统。与基于RDMA的解决方案相比,Beluga-KVCache在vLLM推理引擎的首次令牌时间(TTFT)上实现了89.6%的缩短,吞吐量提升了7.35倍。据我们所知,Beluga 是首个允许 GPU 通过 CXL 交换机直接访问大规模内存池的系统,标志着 GPU 向低延迟、共享庞大内存资源的重大进展。“

研发:基于FPGA的分布式共享内存架构支持CXL 2.0+规范

论文提出了支持CXL 2.0+规范的基于FPGA的分布式共享内存架构。

《网络与并行计算》发表了一篇由黄秀浩、丁金格、刘海坤、段卓辉、廖晓菲 、海金撰写的文章,作者包括华中理工大学计算机科学与技术学院大数据技术与系统工程研究中心、服务计算技术与系统实验室/集群与网格计算实验室, 430074,中国武汉

摘要:“大数据和人工智能应用对传统的分布式共享内存架构构成重大挑战,网络带宽和延迟限制已成为关键瓶颈。尽管计算快递链路(CXL)协议承诺实现低延迟、高带宽的内存扩展互联,但现有的CXL 1.1设备仍无法支持跨多节点的细粒度内存共享。本文提出了一种基于FPGA的分布式共享内存架构,支持CXL 2.0+规范。它在透明跨节点内存访问方面具有三项关键创新:1)用CXL物理链路替代传统网络栈,以减轻频繁数据复制的性能开销;2)硬件管理的内存控制器,采用交错访问机制,优化CXL-DDR通道的带宽利用;3)分层队列,确保在高并发状态下内存访问顺序。这种细粒度内存共享架构支持通过引用传递方式在多台服务器间进行零复制数据交换。实验结果显示,基于CXL的共享内存架构的端到端访问延迟最低为(1.25,upmu text {s}),比单边远程直接内存访问(RDMA)低5倍(times )。

研发:Sangam,基于芯片组的基于芯片组的 DRAM-PIM 加速器,支持基于 CXL 集成用于 LLM 推理Work

该模块通过将逻辑和内存解耦到异构技术节点制造并通过中介器连接的芯片组,解决了芯片组的限制。

ArXiv发表了一篇由Khyati Kiyawat、范振兴、Yasas Seneviratne、Morteza Baradaran、Akhil Shekar、Zihan Xia、Mingu Kang、Kevin Skadron、弗吉尼亚大学、加州大学圣地亚哥分校、美国的作者撰写的文章。

摘要:“由于模型规模的增加,大型语言模型(LLMs)数据量日益增加,随着上下文长度及键值(KV)缓存大小的增加,它们也变得内存受限。推理,尤其是解码阶段,主要由内存受限的GEMV或低作强度(OI)的平面GEMM作主导,因此非常适合内存处理(PIM)方法。然而,现有的内存内/近内存解决方案面临关键限制,如由于在DRAM芯片内集成处理元件(PE)的面积成本高而导致内存容量降低,以及由于DRAM制造技术限制导致PE能力有限。这项工作提出了一种基于芯片组的内存模块,通过将逻辑和内存解耦成在异构技术节点制造并通过中介器连接的芯片组中,解决了这些限制。逻辑芯片组支持对存储存储库的DRAM芯片组的高带宽访问,并集成了系统阵列和基于SRAM的缓冲区等先进处理组件,以加速内存受限的GEMM内核,这些能力在之前的PIM架构中是不可行的。我们提出Sangam,这是一种基于芯片组的CXL连接PIM芯片组内存模块,可以作为GPU的直接替代,也可以与GPU协同执行。Sangam在LLaMA 2-7B、Mistral-7B和LLaMA 3-70B上,端到端查询延迟分别提升了3.93、4.22、2.82倍,解码吞吐量提升了10.3倍、9.5倍、6.36倍,并且在不同输入大小、输出长度和批处理大小方面节省了数量级的能源效率。”

研发:用支持CXL的空闲I/O带宽采集

作者介绍SURGE,一种软件支持的架构技术,通过挽救空闲的I/O带宽资源提升内存带宽可用性。

ArXiv 发表了一篇由美国佐治亚理工学院电气与计算机工程学院的 Divya Kiran Kadiyala 和佐治亚理工学院计算机科学学院的 Alexandros Daglis 撰写的文章。

摘要:“服务器级CPU核心数量的持续增加,增加了对内存系统的需求,而这些系统受限于芯片外引脚和数据传输速率的可扩展性。因此,高端处理器通常具有较低的核心内存带宽,从而降低了内存密集型工作负载。我们提议通过提升CPU有限引脚的实用性来缓解这一挑战。在典型的CPU设计过程中,可用引脚分配给内存和I/O流量,每个引脚约占总片外带宽的一半。因此,除非内存和I/O同时被高度利用,否则这种碎片化会导致宝贵的片外带宽资源被严重利用。理想的架构应提供输入输出和内存带宽的可互换性,允许根据每个工作负载使用片外总带宽。”

“在本研究中,我们介绍了SURGE,一种软件支持的架构技术,通过回收闲置的I/O带宽资源来提升内存带宽可用性。SURGE利用多功能互连技术(如CXL)的能力,在同一处理器接口上动态复用内存和I/O流量。我们证明,SURGE增强架构在带宽受限的服务器上,能将内存密集型工作负载加速最多1.3倍。“

声明: 此文观点不代表本站立场;转载须要保留原文链接;版权疑问请联系我们。