UCIe 2.0 规范是一个开放标准,比一年前发布的 UCIe 1.1 规范更快、更节能,使芯片制造商采用 3D 封装成为可能。

未来从工厂出来的先进芯片将随着新的互连规格而变得明显更快,该规格可以提供比其前代产品高出75倍的带宽。 Universal Chiplet Interconnect 2.0 (UCIe 2.0) 是紧密封装在 3D 结构中的下一代芯片的最新规格。

更紧凑的设计将在速度和功率效率方面提供前所未有的改进。

“这一切都是为了让事情变得简单——提供大量的带宽,但功率却非常少,而且......我们都会走在前面,“制定UCIe规范的UCIe联盟主席Debendra Das Sharma说。

促进向 3D 设计的转变

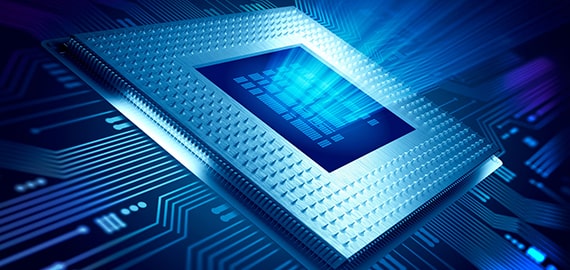

芯片制造行业正在转向 3D 设计,其中芯片是垂直堆叠的。3D结构具有执行不同功能的微型芯片(称为小芯片),这些芯片将使用UCIe 2.0协议进行通信。

“到2028年,小芯片和芯片系统将超越单片芯片,”英特尔铸造厂高级副总裁凯文·奥巴克利(Kevin O'Buckley)在英特尔网站上发表的一份公开声明中说。英特尔没有引用这些数字的来源。

UCIe 1.1 规范是为 2D 结构中的芯片设计的,但 2.0 规范是第一个针对 3D 结构的规范,其中小芯片彼此相邻堆叠。

三维结构将促进小芯片之间的更多通信通道,而在二维结构中,小芯片必须线性通信。

3D封装可以计算芯片内部的元素。如今的 PC 和服务器已经集成了内存、CPU、GPU、AI 内核和电源管理控制的混合体。

“你会看到巨大影响的两件主要事情是带宽和电源效率,”Das Sharma说。

UCIe 2.0 规范是一个开放标准,比一年前发布的 UCIe 1.1 规范更快、更节能。

UCIe 2.0 规范还使芯片制造商采用 3D 封装成为可能。台积电、三星和英特尔拥有自己的封装技术,但也在努力支持彼此的技术。

新规格还为将连接器直接插入基板打开了大门。例如,许多公司计划在基板中实施更新的光互连,以便小芯片可以以更快的速度进行通信。

UCIe 联盟成员包括设备和芯片制造商的名人录,包括 Nvidia、Intel、AMD、Google 和 TSMC。苹果不是其成员,但预计将通过台积电封装采用3D结构。该联盟成立于2022年。

更快、更节能

3D 结构中的小芯片的凸起间距高达 1 微米,比 2.5D 结构的 25-55 微米要近得多。

较小的凸点间距对于创建更小的芯片封装至关重要,从而通过连接小芯片的更多导线实现更快的带宽。

“如果我的凸起间距为 5 微米,然后我下降到 1 微米,那么在给定区域中,我的电线数量是原来的 25 倍,”Das Sharma 说。

UCIe 2.0 协议将支持每通道高达 4 GT/s 的传输速度,与 UCIe 1.1 规范相同。但是小芯片将有更多的电线需要连接——就像更多的内存通道一样——并且彼此之间的距离会更近。

这增加了带宽密度并减少了传输数据所需的功率。

每个小芯片都有自己的通信组件 - NOC(片上网络) - 可加速小芯片之间的通信。

“我们从每平方毫米每秒 4000 千兆字节开始,一旦我们达到一微米,我们就会一直达到每秒 300,000 千兆字节——或每秒 300 TB,这是巨大的带宽,”Das Sharma 说。

UCIe 1.1 带宽为 165 – 1317 GB/s,但使用 UCIe 2.0 时,没有限制,因为更多的电线将连接小芯片。

小芯片之间的距离更短,也使其比 UCIe 1.1 或行业标准互连的能效更高。

“这个东西有助于我们提高电源效率,因为我的距离更小......而且我没有太多的电路,“Das Sharma说。

UCIe 2.0 预计每比特消耗 0.05 皮焦耳, 在 1 微米凸起间距下降至每比特 0.01 皮焦耳。

“如果你研究PCI Express或以太网,每比特是5到10皮焦耳,这取决于谁在做设计,”Das Sharma说。

UCIe 2.0 具有新的工具,可用于在小芯片的整个生命周期中对其进行管理、发现和测试。它有助于小芯片的验证、部署和升级过程。这将使芯片制造商能够处理与小芯片制造和性能相关的问题。

UCIe在一份规格文件中表示:“UCIe 2.0中的DFX功能提供了一种标准化的方法,可以提高不同小芯片设计和制造商的可测试性、可制造性和可靠性。

该规范将支持 CXL、PCIe 和其他已知互连。然而,包括 Nvidia 和 Ayar Labs 在内的许多公司正在开发自己的互连,他们可以将其置于 UCIe 2.0 之上。

“你也可以在此基础上映射你自己的专有协议 - 有些人想将其用于他们自己的扩展型连接,”Das Sharma说。

产品时间线

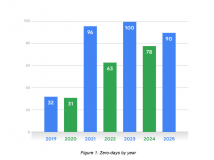

基于UCIe 2.0的芯片何时进入市场没有明确的时间表,但这需要时间。 UCIe 1.0 互连还远未实现,英特尔去年展示了其在 Intel 3 工艺上制造的测试芯片。

“各个成员公司根据自己的潜在客户来决定......如果有一个明确定义的规范,他们就可以实施它,然后他们就会把产品出来,“Das Sharma说。

UCIe 联盟每一年发布一次新的规范,但 2.0 的后续规范何时发布没有明确的时间表。

Das Sharma表示,对UCIe 2.0有足够的需求,因此发布了规格。

UCIe还成立了工作组,将互连扩展到寻求更快连接以安装在汽车中的汽车公司。

声明: 此文观点不代表本站立场;转载须要保留原文链接;版权疑问请联系我们。